4.2. Condition Codes¶

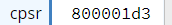

The ARM processor maintains a special register known as the Current Program Status Register or CPSR.

The CPSR is used to track information about what mode the processor is in and the result of recent instructions.

In particular, the upper 4 bits of the register are used to track the following information:

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| N | Z | C | V | operating mode | |||||||||||||||||||||||||||

N Was the result negative?

Z Was the result zero?

C Was there a carry out of the leftmost bit? (Though this bit is used in complex ways that do not always mean carry.)

V Was there mathematical overflow? (For signed math this is not the same as having a carry out of the leftmost bit.)

Tip

The exact rules for setting the carry bit are complex and depend on the type of comparison instruction being executed. You are not responsible for the details, just recognize that the carry bit does not always mean a literal carry.

These values are only set by specific instructions. The most straightforward of these instructions is compare:

CMPrn, rm / #CoMPare. Subtract rm or # by from rn and update the status registers based on the results. The result of the subtraction is ignored.

In this code sample below the value 10 is compared with something larger, something smaller, and itself. The only result of

running the CMP instructions is to change the CPSR.

1 2 3 4 5 6 7 8 9 10 11 12 13 | MOV r1, #10 @load x's address

CMP r1, #20 @do r1 - 20, set result bits

@result bits are now 0x8 or 0b1000 : only Negative is set

CMP r1, #2 @do r1 - 2, set result bits

@result bits are now 0x2 or 0b0010 : only carry bit was set

CMP r1, #10 @do r1 - 10, set result bits

@result bits are now 0x6 or 0b0110 : carry and zero bits are set

end:

B end @stop here

|